TUGAS MAKALAH

“MODE TIMER”

OLEH

AGUNG ARIEZ PERDANA PUTRA

323 13 025

2A ELEKTRONIKA

JURUSAN TEKNIK ELEKTRO PRODI ELEKTRONIKA

POLITEKNIK NEGERI UJUNG PANDANG

2015/2016

KATA PENGANTAR

Puji syukur

penyusun panjatkan ke hadirat Allah Subhanahu wata’ala, karena berkat

rahmat-Nya kami bisa menyelesaikan makalah yang berjudul Mode Timer. Makalah

ini diajukan guna memenuhi tugas mata kuliah Mikrokontroler.

Kami mengucapkan

terima kasih kepada semua pihak yang telah membantu sehingga makalah ini dapat

diselesaikan tepat pada waktunya. Makalah ini masih jauh dari sempurna, oleh

karena itu, kritik dan saran yang bersifat membangun sangat kami harapkan demi

sempurnanya makalah ini.

Semoga makalah

ini memberikan informasi bagi masyarakat dan bermanfaat untuk pengembangan

wawasan dan peningkatan ilmu pengetahuan bagi kita semua.

Makassar, 8 Mei 2015

Penyusun

BAB I

PENDAHULUAN

Latar belakang

AVR

merupakan seri mikrokontroler CMOS 8-bit buatan Atmel, berbasis arsitektur RISC (Reduced Instruction Set Computer).

Hampir semua instruksi dieksekusi dalam satu siklus clock. AVR mempunyai 32 register general-purpose,

timer/counter fleksibel dengan mode compare,

interrupt internal dan eksternal, serial UART, programmable Watchdog Timer, dan mode power saving, ADC dan PWM

internal. AVR juga mempunyai In-System

Programmable Flash on-chip yang mengijinkan memori program untuk

diprogram ulang dalam sistem menggunakan hubungan serial SPI. ATMega16. ATMega16

mempunyai throughput mendekati

1 MIPS per MHz membuat disainer sistem untuk mengoptimasi konsumsi daya versus kecepatan

proses.

Batasan

Masalah

1. Menjelaskan

tentang mode timer pada mikrokontroler ATMega16.

2. Memaparkan

fungsi dari setiap mode timer pada mikrokontroler ATMega16.

Tujuan

1. Ingin

mengetahui tentang mode timer pada mikrokontroler ATMega16.

2. Untuk mengetahui

fungsi mode timer pada ATMega16.

BAB II

PEMBAHASAN

Timer

Timer/counter adalah fasilitas dari ATMega16 yang digunakan untuk

perhitungan pewaktuan. Beberapa fasilitas chanel dari timer counter

antara lain: counter channel tunggal,

pengosongan data timer sesuai dengan data pembanding, bebas -glitch, tahap yang tepat Pulse Width

Modulation (PWM), pembangkit frekuensi,

event counter external..

Gambaran Umum

Gambar diagram block timer/counter

8 bit ditunjukan pada gambar 2. Untuk penempatan pin I/O telah di jelaskan pada

bagian I/O di atas. CPU dapat diakses register I/O, termasuk dalam pin-pin I/O

dan bit I/O. Device khusus register

I/O dan lokasi bit terdaftar pada deskripsi timer/counter 8 bit.

Gambar 2 Blok diagram timer/counter

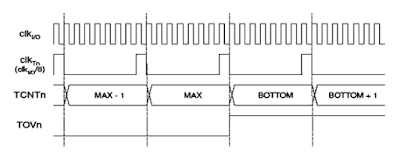

Timing Diagram Timer/Counter

Timer/counter didesain sinkron clock

timer (clkT0) oleh karena itu ditunjukkan sebagai sinyal enable clock pada gambar 3. Gambar ini

termasuk informasi ketika flag interrupt dalam

kondisi set. Data timing digunakan sebagai dasar dari operasi timer/counter.

Gambar 3 Timing diagram timer/counter, tanpa

prescaling

Sesuai dengan gambar 4 timing diagram timer/counter dengan prescaling

maksudnya adalah counter

akan menambahkan data counter (TCNTn) ketika terjadi pulsa clock telah mencapai 8 kali pulsa dan

sinyal clock pembagi aktif clock dan ketika telah mencapai nilai

maksimal maka nilai TCNTn akan kembali ke nol. Dan kondisi flag timer akan aktif ketika TCNTn maksimal.

Gambar 4 Timing diagram timer/counter, dengan

prescaling

Sama halnya timing timer diatas, timing timer/counter dengan seting OCFO

timer mode ini memasukan

data ORCn sebagai

data input timer. Ketika nilai ORCn sama dengan nilaiTCNTn maka pulsa flag timer akan aktif. TCNTn akan

bertambah nilainya ketika pulsa clock telah

mencapai 8 pulsa. Dan kondisi flag akan

berbalik (komplemen) kondisi ketika nilai TCNTn kembali kenilai 0 (overflow).

Gambar 5 Timing diagram timer/counter, menyeting OCFO,

dengan pescaler

(fclk_I/O/8)

Ketika nilai ORCn sama dengan nilai TCNTn maka pulsa flag timer akan aktif. TCNTn akan

bertambah nilainya ketika pulsa clock telah

mencapai 8 pulsa. Dan kondisi flag akan

berbalik (komplemen) kondisi ketika nilai TCNTn kembali kenilai 0 (overflow).

Gambar 6 Timing diagram timer/counter, menyeting OCFO,

pengosongan data timer sesuai dengan data pembanding,dengan pescaler

(fclk_I/O/8)

Deskripsi Register Timer/Counter

8 bit

Gambar 7 Regiter timer counter 8 bit

Bit 7 – FOCO :

perbandingan kemampuan output

FOCO hanya akan

aktif ketika spesifik-spesifik bit

WGM00 tanpa PWM mode. Adapun untuk meyakinkan terhadap kesesuaian

dengan device-device yang akan

digunakan, bit ini harus diset nol

ketika TCCRO ditulisi

saat mengoperasikan mode

PWM. Ketika menulisi logika satu

ke bit FOCO, dengan segera dipaksakan untuk disesuaikan pada unit pembangkit bentuk gelombang. Output OCO diubah

disesuaikan pda COM01: bit 0

menentukan pengaruh daya pembanding.

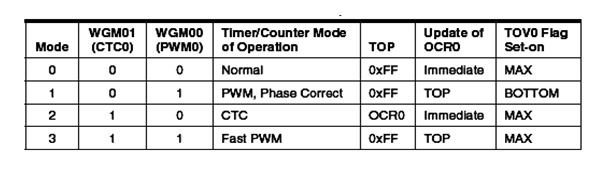

Bit 6,3 – WGM01:0:

Waveform Generation Mode

Bit ini mengontrol penghitungan yang teratur pada counter, sumber untuk

harga counter maksimal ( TOP )., dan

tipe apa dari pembangkit bentuk gelombang yang digunakan. Mode-mode operasi

didukung oleh unit timer/counter sebagai berikut : mode normal, pembersih timer

pada mode penyesuaian dengan pembanding ( CTC ), dan dua tipe mode Pulse Width Modulation ( PWM ).

Tabel 2

Deskripsi Bit Mode Pembangkit Bentuk Gelombang

catatan: definisi nama-nama bit CTC0 dan PWM0 sekarang tidak

digunakan lagi. Gunakan WGM 01: 0 definisi. Bagaimanapun lokasi dan fungsional

dan lokasi dari masing-masing bit sesuai dengan versi timer sebelumnya.

Bit 5:4 – COMO1:0

Penyesuaian Pembanding Mode Output

Bit ini mengontrol pin output compare

(OCO), jika satu atau

kedua bit COM01:0

diset, output OC0

melebihi fungsional port normal I/O dan keduanya terhubung juga.

Bagaimanapun, catatan bahwa bit Direksi

Data Register (DDR) mencocokan ke pin OC0 yang mana harus diset dengan

tujuan mengaktifkan. Ketika OC0 dihubungkan ke pin, fungsi dari bit COM01:0

tergantung dari pengesetan bit WGM01:0.

Tabel di bawah

menunjukkan COM fungsional ketika bit-bt WGM01:0 diset ke normal atau mode CTC (non PWM).

Tabel 3 Mode

Output Pembanding, tanpa PWM

Tabel 4 menunjukan bit COM01:0

fungsional ketika bit WGM01:0

diset ke mode fast PWM.

Tabel 4 Mode

Output Pembanding, Mode fast PWM

Tabel 5

menunjukan bit COM01:0

fungsional ketika bit WGM01:0 diset ke mode

phase correct PWM.

Tabel 5 Mode Output Pembanding, Mode phase correct PWM

Bit 2:0 – CS02:0 :

Clock Select

Tiga bit clock select sumber clock digunakan dengan timer/counter.

Jika mode pin eksternal digunakan

untuk timer counter0, perpindahan dari pin T0 akan memberi clock counter.

Tabel 6 Deskripsi bit clock select

Sesuai dengan tabel diatas maka sumber clock dapat dibagi sehingga timer/counter dapat disesuaikan dengan

banyak data yang dihitung.

Register Timer/Counter TCNT0

Gambar 8 Register timer TCNT0

Register timer/counter

memberikan akses secara langsung, keduanya digunakan untuk membaca dan

menulis operasi, untuk penghitung

unit 8-bit timer/counter. Menulis

ke blok-blok register TCNT0 (removes) disesuaikan dengan clock timer

berikutnya. Memodifikasi counter

(TCNT0) ketika perhitungan berjalan, memperkenalkan resiko

kehilangan perbandingan antara

TCNC0 dengan register OCR0.

Register Timer/Counter OCR0

Gambar 9. Register timer OCR0

Register output pembanding

berisi sebuah haraga 8 bit yang mana secara terus-menerus dibandingkan

dengan harga counter (TCNT0).

Sebuah penyesuaian dapat

digunakan untuk membangkitkan

output interrupt pembanding, atau

untuk membangkitkan sebuah output bentuk gelombang pada pin OC0.

Register Timer/Counter Interrupt Mask

Bit 1-OCIE0: output

timer counter menyesuaikan dengan kesesuaian interrupt yang aktif.

Ketika bit OCIE0 ditulis

satu, dan 1-bit pada register

status dalam kondisi set

(satu), membandingkan timer/counter pada interrupt

yang sesuai diaktifkan.

Mencocokkan interrupt yang

dijalankan kesesuaian pembanding

pada timer/counter0 terjadi, ketika bit OCF0 diset pada register penanda timer/counter-TIFR.

Bit 0 – TOIE0:

Timer/Counter 0 Overflow Interrupt Enable

Ketika bit TOIE0 ditulis

satu, dan 1-bit

pada register status dalam

kondisi set (satu), timer/counter melebihi interrupt

diaktifkan. Mencocokkan interrupt dijalankan

jika kelebihan pada timer/counter0 terjadi, ketika bit TOV0 diset pada register

penanda timer/counter- TIFR

Register Timer/Counter

Register - TIFR

Gambar 10 Register timer TIFR

Bit 1 – OCF0: Output

Compare Flag 0

OCF0 dalam kondisi set (satu) kesesuaian pembanding terjadi antara

timer/counter dan data pada OCRO – Register 0 keluaran pembanding. OCF0 diclear

oleh hardware ketika eksekusi

pencocokan penanganan vector interrupt.

Dengan alternatif mengclearkan OCF0 dengan menuliskan logika satu pada flag. Ketika I-bit pada

SREG, OCIE0 (Timer/Counter0 penyesuaian

pembanding interrupt enable), dan OCF0

diset (satu), timer/counter pembanding

kesesuaian interrupt dijalankan.

Bit 0 – TOV0:

Timer/Counter Overflow Flag

Bit TOV0 diset (satu) ketika kelebihan terjadi pada timer/counter0. TOV0

diclearkan dengan hardware ketika

penjalanan pencocokan penanganan vector

interrupt. Dengan alternatif, TOV0 diclearkan dengan jalan memberikan

logika satu pada flag. Ketika I- bit

pada SREG, TOIE0

(Timer/Counter0 overflow

interrupt enable), dan TOV0

diset (satu ), timer/counter overflow interrupt

dijalankan. Pada tahap mode PWM yang tepat, bit ini di set ketika timer/counter

merubah bagian perhitungan pada $00.

BAB III

PENUTUP

Timer/counter didesain sinkron clock

timer (clkT0) oleh karena itu ditunjukkan sebagai sinyal enable clock.

Ketika nilai ORCn sama dengan nilaiTCNTn maka pulsa flag timer akan aktif. TCNTn akan bertambah nilainya ketika pulsa clock telah mencapai 8 pulsa. Dan kondisi flag akan berbalik (komplemen) kondisi ketika nilai TCNTn kembali kenilai 0 (overflow).

Register timer/counter memberikan akses secara langsung, keduanya digunakan untuk membaca dan menulis operasi, untuk penghitung unit 8-bit timer/counter. Menulis ke blok-blok register TCNT0 (removes) disesuaikan dengan clock timer berikutnya. Memodifikasi counter (TCNT0) ketika perhitungan berjalan, memperkenalkan resiko kehilangan perbandingan antara TCNC0 dengan register OCR0.

DAFTAR PUSTAKA

Sholihin, M. (2008). Mengenal Mikrokontroler AVR

ATMega16. [Online]. Tersedia: http://ilmukomputer.org/wp-content/uploads/2008/08/sholihul-atmega16.pdf.

Html [8 Mei 2015].

Makalah tersebut bisa di download disini